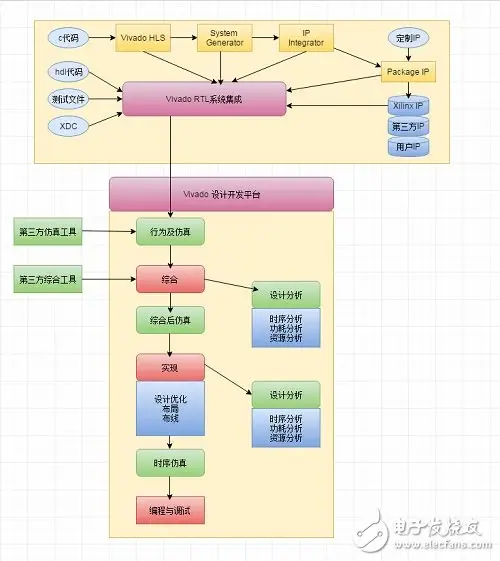

在电子设计界,FPGA(现场可编程门阵列)的开发变得越发关键。不过,它的软件开发流程看起来挺复杂。这对众多开发者来说,是个不小的难题。但只要掌握了它,就能发现其中的巨大价值。

代码输入

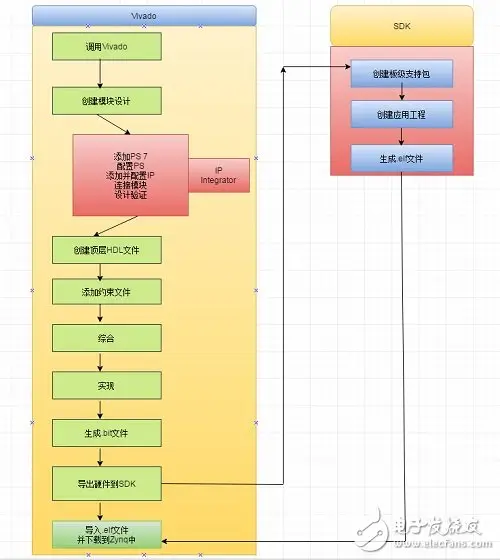

FPGA开发的第一步是输入代码。开发者需在特定设计环境中操作,例如,在许多企业的研发部门,他们常用VHDL或Verilog等硬件描述语言。这要求开发者对这些语言有深入的了解。举个例子,若要开发计数器,必须用精确的代码来实现计数功能。此外,不同项目可能有各自的代码规范,特别是在跨国企业的开发项目中,对代码规范的审查非常严格。

编写代码时也可能遇到不少难题,诸如语法上的失误。这种情况在新手程序员中较为常见,因为他们对语法规则不够熟悉,这往往使得他们输入的代码无法顺利进入后续的处理环节。

功能仿真

功能仿真对于检测代码能否达到预定效果至关重要。众多大型电子设备生产企业设有专门的仿真实验室。在此过程中,会对输入代码施以测试信号,以观察其输出结果是否达标。比如,在开发交通信号灯控制系统时,通过功能仿真,可以模拟不同车辆流量和时间间隔,检验信号灯的切换是否准确。

有时候,功能仿真的效果和预期不符,这时开发者就得重新审视代码。这可能是由于对逻辑的理解出现了偏差,或是代码中存在逻辑上的缺陷,需要细心地逐行查找问题。

综合

综合步骤是关键,它负责将代码转换成基础逻辑单元的连接。在许多专业FPGA开发室,人们会运用特定的综合工具来完成这一过程。这一步骤将我们的代码或原理图转换为由基础逻辑单元,比如与门、或门、非门等构成的逻辑连接。这就像将建筑蓝图转换成建筑材料的清单一样。

在综合过程中,会依据一定的限制条件对形成的逻辑关系进行优化调整。若这些限制条件设定不恰当,可能会导致最终形成的逻辑关系无法实现最佳性能。比如,对时钟频率这类关键参数的设置若不准确,将影响整个FPGA的运行效能。

综合后仿真

综合后的效果需要经过模拟验证。这一环节在大学的研究项目中至关重要,它能保证综合后的逻辑是否依旧符合功能需求。由于综合过程中可能因优化等操作而改变原有逻辑,这种模拟检验便能及早发现潜在问题。

遇到综合仿真的问题时,我们得重新检查综合步骤中的限制规定或代码规则。这要求开发者能准确识别出错环节,并迅速进行更正。

实现

在实现阶段,我们需进行映射、布局和布线等工作。许多科技企业会借助专业工具来完成这一流程。具体来说,映射是指将网表中的逻辑门转换成实际物理元素,例如将逻辑设计分配到FPGA内部的逻辑块等资源中。

整体布局涉及对逻辑单元的宏观定位,而布线工作则是对这些单元进行细致的连接。这两个步骤都依赖于特定的算法,若算法不当,可能会导致逻辑连接出现障碍,进而影响整体效果。

布线后仿真与验证

布线完成之后,需要进行仿真和验证来检查其是否能够正常运行。这个环节在众多电子产品开发项目中是常见的。布线后可能会出现延迟等问题,而仿真验证则是确保成品在实际使用中不会出现故障的关键步骤。

要找出问题根源,得回溯到布线设计阶段,探究原因。这可能是由于布线资源分配不当,或是布线通道出现了拥堵等情况。

各位,我来提个问题:在FPGA的开发阶段,大家觉得哪个部分最容易出错?欢迎留言交流,点个赞,或者转发一下。

完成这些步骤后,便要进行最后的在线调试,或者把配置文件写入芯片进行测试。FPGA软件开发的全过程紧密相连,每个环节都需开发者精心操作和核实,这样才能保证最终产品的顺利运行。